Astronomical CCD Observing and Reduction Techniques ASP Conference Series, Vol. 23, 1992 Steve B. Howell, ed.

# HISTORY AND ADVANCEMENTS OF LARGE AREA ARRAY SCIENTIFIC CCD IMAGERS

James Janesick, Tom Elliott

Jet Propulsion Laboratory

California Institute of Technology

CCD Advanced Development Group

4800 Oak Grove

M.S. 300/315-K

Pasadena, Ca. 92209

Tel. 818-354-7734

#### **ABSTRACT**

This paper summarizes progress made in the past eighteen years in the development of the scientific charge-coupled device at JPL in collaboration with several CCD manufacturers and foundries. We examine advancements made since its conception, its current achievements, and report on new performance limitations for the sensor in the future. We discuss how these very useful devices work and examine new physical understandings behind their most remarkable characteristics. Some of these subjects include: array and pixel size, quantum efficiency, quantum yield, charge collection efficiency, charge transfer efficiency, read noise, dark current, full well capacity, anti-blooming, residual image, and tolerance to radiation damage. New test tools developed to measure these characteristics are also introduced.

#### 1. INTRODUCTION

Charge-coupled devices (CCDs) were first introduced to the world in 1970 in a pair of papers by Boyle and Smith in the Bell System Technical Journal (1,2). CCDs were initially conceived as an electronic analogue of the magnetic bubble device. In order to function as memory, there must be a physical quantity which represents a bit of information, a means of recognizing the presence or absence of the bit (reading), and a means of creating and destroying the information (writing and erasing). In the CCD, a bit of information is represented by a packet of charges (electrons (e-) or holes (h+)). These charges are stored in the depletion region of a metal insulator semiconductor (MIS) capacitor, important CCD structures to be described below. Charges are moved about in the CCD circuit by placing the MIS capacitors very close to one another and manipulating the voltages on the gates of the capacitors so as to allow the charge

to spill from one capacitor to the next: thus the name charge-coupled device (3). A charge detection amplifier detects the presence of the charge packet providing a useful voltage to the outside world. Charge packets can be created by injecting charge from a diode adjacent to a CCD gate. Like the magnetic bubble device, the CCD is a serial device where charge packets are read one at a time.

Although the original concept of the CCD was a memory device, it became immediately clear to a large number of workers in the semiconductor field that the CCD had potential uses that ranged far wider than simple memory applications. During the past two decades, the primary goal of CCD manufacturers has been to develop CCD sensors to replace tube type sensors (e.g., vidicon The emphasis has been on realizing the CCD's advantages low-power consumption, ultra-low-noise, weight, linearity, dynamic range, photometric accuracy, broad spectral response, geometric stability, reliability and durability, while attempting to match tube characteristics in format, frame rate, cosmetic quality, and cost. As a consequence, most home video cameras are now based on CCD sensors where only a few years ago tube imagers were mostly used. Photographic film is rapidly taking a back seat to the new sensor where solid state color CCD still cameras (e.g. 35 mm) are now commercially available (e.g., Although relatively expensive, by the end of the century a low-cost color "instamatic" CCD type camera is expected.

# Early Astronomy and CCDs

Astronomers, with their fundamental interest in the detection of photons from far away places, were perhaps the first to recognize the potential of the CCD for high quality scientific imaging. comparison to photographic film and SEC vidicon tubes already in use, CCDs offered several benefits to the astronomer. workers at the Jet Propulsion Laboratory initiated a program to develop high performance large area array CCDs, designed for space-borne navigation and imaging instruments. To promote interest about the CCD in the scientific community the JPL team built a Traveling CCD Camera System, the first of its kind, to be used at major astronomical observatories worldwide. At the time astronomers and engineers were not familiar with the new chip and were basically content with photographic films and vidicon tubes currently in use. JPL management recognized that scientists should become familiar with the capabilities and unique features of the CCD to help promote and support future NASA imaging missions. Expeditions flight projects for to various observatories with the new camera system paid off as the CCD expectations. performed beyond anyone's New scientific

discoveries were usually made each time the camera system visited a new site.

Following these visits the demand for the CCD became intense Simply put, those who had access to a CCD among astronomers. chip had the advantage in generating new science. would never be the same for the CCD was about to revolutionize astronomical instrumentation much as film did nearly 100 years Within a few years the CCD became the sensor of choice at all major observatories (with the possible exceptions of Schmidt telescopes like the 48-inch Mt. Palomar telescope that utilize large photographic plates). Also CCDs utilized at observatories could participate and produce new science that at one time could only be generated by larger telescopes. sensitivity of 100 times faster than film, it was clear that more data could be produced in a shorter period of time using a CCD. The new sensor immediately set new records in seeing the most distant and dimmest objects in the universe, objects that were invisible to film and tube type detectors before.

## NASA Space-born CCD Imaging Missions

Following the introduction of the CCD to the scientific community several new NASA/JPL proposals were written and awarded in using the sensor in space-born imaging instruments. Many NASA missions currently in space are based on CCDs. For example, JPL's Wide Field/Planetary Camera (WF/PC I) on board the Hubble Space Telescope (HST) utilizes eight Texas Instruments 800 x 800, 15micron picture element (pixel), 3-phase CCDs (TI)3PCCD). Although the spherical aberration problem permanently built into the primarily 94-inch mirror of Hubble is significantly limiting scientific return, the cameras and CCDs are performing expectation. For example, the camera has returned gorgeous color photos of the planets Jupiter, Saturn, and Pluto with 0.1 arc-sec resolution employing image processing techniques to remove the spherical aberration in the images caused by the mirror. WF/PC II cameras currently under construction at JPL with builtcorrective optics will use new state-of-the-art fabricated by Loral Aeronutronic Inc. (formally Ford Aerospace in Newport Beach Ca.). The JPL Solid State Imaging (SSI) camera aboard the spacecraft Galileo in route to Jupiter uses a single Texas Instruments 800 x 800, 15-micron pixel, virtual-phase CCD (TI VPCCD). Galileo may too have a potentially dangerous flaw with its high-gain antenna which would significantly limit the number of CCD images sent back from Jupiter (the data rate of Galileo's working low-gain antenna is limited to only 10 bits/sec at Jupiter requiring several hours to send a single image). Currently Galileo's camera and CCD are functioning flawlessly generating excellent images of Venus, Earth, Moon and also a

single image of asteroid Gaspra. Most of the asteroid pictures will be transmitted by Galileo's low-gain antenna when the spacecraft swings by earth a year from now before heading to Jupiter. The JPL Solar X-ray Telescope (SXT) camera aboard the Japanese Solar-A spacecraft utilizes a single 1024 x 1024, 18micron pixel VPCCD to observe x-ray emission from the sun. launched in August of 1991 and is generating spectacular high resolution x-ray movies of the sun. camera constructed last year at the Lyndon B. Johnson Space Center has recently been flown on the Space Shuttle (September, 1991, STS-48) for NASA's Electronic Still Camera Project (ESC). The solid state camera, a modified Nikon 35-mm body, utilizes a 1024 x 1024, 15-micron pixel Loral CCD. Numerous high resolution black and white images of the shuttle and astronauts were generated.

Other NASA missions that plan to use the CCD include MIT/Penn-State's Advanced CCD Imaging Spectrometer (ACIS) employed on the Advanced X-ray Astrophysics Facility (AXAF). The instrument will generate high resolution x-ray images of active galaxies, super novas, quasars, etc. and simultaneously measure the energy of Several high performance 420 x 420 pixel CCDs incident x-rays. fabricated by Lincoln Laboratory will be utilized in AXAF's focal plane. It is hoped that AXAF will be launched before the turn of the century. NASA's Mars Observer (MO) is a CCD imaging mission to planet Mars scheduled for launch next year (1992). camera is being built at the California Institute of Technology using two linear Loral CCDs (1 x 2048 and 1 x 3456 pixels). NASA's two newest planetary missions are: Comet Rendezvous Asteroid Flyby (CRAF) and Cassini. CRAF will obtain close-up views of a comet (comet Kopff) and an Asteroid (to be determined) using three imaging cameras (referred to as the Imaging Science Subsystem (ISS)) that utilize 1024 x 1024, 12-micron pixel threephase CCDs fabricated by Loral. The imaging cameras aboard Cassini are identical to CRAF except for the spectral filters used. Cassini also carries a small probe to image Saturn's large The probe camera will use a custom Loral 512 x 512 pixel CCD. Also an Italian instrument, the Visual and Infrared Mapping Spectrometer (VIMS) cameras on board CRAF/Cassini will use CCDs similar to the ISS CCDs. The CRAF/Cassini spacecraft will be built and managed by JPL. The Space Telescope Imaging Spectrometer (STIS), a second generation ST camera, will utilize Tektronix CCDs. Originally the mission was to use two large 2048 21-micron pixel Tektronix three-phase illuminated CCDs. However, recent budget cuts have reduced the instruments capability to a single 1024 x 1024 pixel Tektronix The instrument and CCD are being developed at Ball device. The Multi-angle Imaging Spectra Radiometer (MISR) cameras will be based on a number of linear Loral CCDs.

an earth observing system consisting of nine cameras to study earth's upper atmosphere. The Cosmic Unresolved X-ray Background with CCDs (CUBIC) camera will use a  $1024 \times 1024$ , 18-micron pixel Loral CCD to study background radiation of the universe in the x-ray. Many other NASA CCD imaging missions are in the proposal stage.

## Paper Contents

paper is divided into eight major chapters: Introduction, (2) CCD theory and Operation, (3) Array and Pixel Size, (4) Quantum Efficiency (QE), (5) Quantum Yield (QY), (6) Charge Collection Efficiency (CCE), (7) Charge Efficiency (CTE), (8) Read Noise, and (9) Frontside Pinning, and (10) CCD Manufacturers and Foundries. We first begin in Chapter 2 with a brief discussion on solid state theory, operation, and basic architecture of the scientific CCD to aid in the discussion of subsequent chapters. In Chapter 3 limitations on CCD array and pixel size will be reviewed. It is in this area of development that the CCD has made its greatest strides. For example, the first commercially available area array CCDs fabricated by Fairchild nearly two decades ago contained 10,000 pixels (i.e., 100 x 100 pixel format). Today CCD arrays with over 16 million pixels (4096 x 4096 pixels) on a single chip can be procured - a factor of 1677 times more pixels than the original Fairchild CCD. There is no fundamental reason why the CCD can't continue to grow in size. Funding and interest are the main factors limiting CCD size currently. In Chapter 4 a discussion on QE performance and limitations for the CCD is QE performance has varied widely addressed. among manufacturers and is the most inconsistent parameter of all CCD performance characteristics. The primary goal manufacturers has therefore been to develop a mature QE technology to achieve high, stable and consistent performance. Chapter 5 reviews the subject of quantum yield or the ability of the CCD to generate multiple e-h hole pairs per interacting photon or particle. This relatively new capability has opened numerous opportunities for the CCD. For example, CCD instruments referred to as CCD radiation imaging spectrometers (CCD-RIS) are used to precisely measure the energy of individual incident radiation events (e.g., photons and ions) and simultaneously In Chapter 6 physical factors that limit CCE image them. performance are discussed. In general CCE for the CCD is wellbehaved and established. Sensors can be fabricated to achieve near theoretical performance in resolving spatial frequencies. However, future improvements are required to minimize charge loss internal to the CCD, an important CCE parameter that will be discussed. For example, CCD-RIS instruments are very vulnerable to charge loss mechanisms exhibited by the CCD. CTE, a very

important CCD parameter, is discussed in Chapter 7. improved to levels that have exceeded everyone's expectation, essentially perfect, and is an area where future development is probably not required. Read noise, discussed in Chapter 7, has also been developed to near perfection. It is unlikely that new breakthroughs will significantly reduce the read noise of the CCD However, we will report on an indirect noise any further. reduction technique recently developed that lowers the noise Chapter 8 also discusses two floor to any level desired. important noise sources generated internal to the CCD. These are dark current generation, an unwanted source of charge that has been significantly reduced in the last two years, and spurious charge a source of charge generated when the CCD is clocked. Chapter 9, miscellaneous but important characteristics about the CCD are discussed: full well capacity, anti-blooming, high-speed erasure, residual image, and radiation damage tolerance. These parameters can be controlled and optimized by a biasing technique referred to as frontside pinning. Chapter 10 presents a list of current scientific CCD manufacturers and foundries.

#### 2. CCD THEORY AND OPERATION

The operation of a CCD is quite simple in principle. An elegant analogy thought up by Morley Blouke (Tektronix) and Jerome Kristian (Mt. Wilson Observatory) is often used to describe how it works. Imagine an array of buckets covering a field. After a rainstorm, the buckets are sent by conveyor belts to a metering station where the amount of water in each bucket is measured. Then a computer would take these data and display a picture of how much rain fell on each part of the field. In a CCD system the "raindrops" are the photons, the "buckets" the pixels, the "conveyor belts" the CCD shift registers and the "metering station" an on-chip amplifier.

Technically speaking the CCD must perform four tasks generating an image. These functions are 1) charge generation, 3) charge transfer, and 4) charge collection, The first operation relies on a physical process known as the photoelectric effect - when photons or particles strikes certain materials free electrons are liberated. A brief discussion of this process associated with the CCD is given In the second step the photoelectrons are collected in the nearest discrete collecting sites or pixels. The collection sites are defined by an array of electrodes, called gates, formed third operation, charge transfer, CCD. The accomplished by manipulating the voltage on the gates in a systematic way so the signal electrons move down the vertical registers from one pixel to the next in a conveyor-belt like

fashion. At the end of each column is a horizontal register of pixels. This register collects a line at a time and then transports the charge packets in a serial manner to an on-chip amplifier. The final operating step, charge detection, is when individual charge packets are converted to an output voltage. The voltage for each pixel can be amplified off-chip and digitally encoded and stored in a computer to be reconstructed and displayed on a television monitor.

#### Photoelectric Effect

Silicon exhibits an energy gap of approximately 1.14 eV which is situated between the valence and the conduction energy bands. Incoming photons can interact with the silicon atoms and excite valence electrons into the conduction band creating electron-hole The e-h pairs created are free to move and diffuse (e-h) pairs. in the silicon lattice structure. The average lifetime for the carriers is on the order of 100 micro-sec or more when generated in quality silicon. After this time the e-h pair will recombine. Photons with energy of 1.1 to 5 eV generate single e-h pairs whereas photons with energy greater than 5 eV produce multiple eh pairs. For example, at Lyman-alpha (1216 A or 10 eV), three eh pairs are generated for each interacting photon on the average. Soft x-ray photons (100 eV - 10 keV) can generate hundreds or thousands of signal electrons making it possible for the CCD to detect single photons.

The useful photoelectric effect for silicon extends over a large spectral range (from  $1.1~{\rm eV}$  to  $10~{\rm keV}$ ). This wavelength range covers the near infrared (NIR), visible, ultra-violet (UV), extreme ultra- violet (EUV), and soft x-ray. The cutoff for near IR photons (less than  $1.1~{\rm eV}$ ) occurs because the photon does not have sufficient energy to elevate a valence band electron to the conduction band. Hence, the silicon is transparent to these photons and are not absorbed. For energies above  $10~{\rm keV}$  the probability of interaction is small, and the silicon atoms again look transparent to these incoming photons.

It should be mentioned that other optical materials can be used to broaden the spectral range of the CCD further. For example, germanium CCDs have been built at Loral which have delivered reasonable performance. Germanium exhibits a band gap of half that of silicon and therefore its IR response is good out to approximately 1.6-microns. In addition, since the density of germanium is greater than silicon, the x-ray response is extended out to about 20 keV.

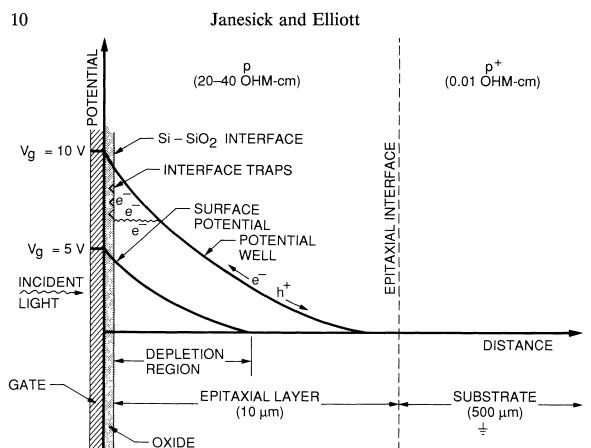

# MIS Capacitor and Depletion

The fundamental building block of the CCD is the MIS capacitor mentioned above (refer to Figure 1). The MIS capacitor can be fabricated on p-type (boron doped) epitaxial silicon on which an insulator layer on the order of 1000 A is grown (composed of silicon dioxide or silicon dioxide and silicon nitride - a dual insulating system). This layer is followed by a conductive gate deposition (typically doped poly silicon). When a positive voltage is applied to the gate, majority carriers (holes) in the silicon are repelled from the region beneath the silicon-silicon dioxide (Si-SiO<sub>2</sub>) interface leaving a depletion region. The potential variation within the depleted silicon is such that a potential well for electrons forms at the surface as shown in Figure 1.

The CCD is composed of an array of closely spaced MIS capacitors There are numerous ways to arrange these capacitors to form Conceptionally the simplest CCD is a three-phase a CCD imager. device, the arrangement that Boyle and Smith used for their first In the three-phase device, a number of gates are arranged in parallel with every third gate connected to the same clock The basic cell in the CCD, which corresponds to one driver. pixel, consists of a triplet of these gates, each separately If one now biases, for connected to phase 1, 2 and 3 clocks. example, phase 1 high (say at 10 V) a depletion region forms and represents a region of higher electrostatic potential relative to the lower biased neighboring gates (say at 5 V). It is under this phase where signal electrons would collect in a pixel. phase where charge collects is referred to as the collecting phase whereas the phases that are biased low are referred to as the barrier phases since they confine charge for the pixel on either side of the collecting phase.

A CCD area array imager can be thought of as many shift registers composed of many pixel elements. The image-forming section of the CCD is covered with closely spaced vertical registers or The columns are separated by implanted potential barriers (called channel-stops) which prevent the spread of the signal charge from one column into the other. Channel-stops are highly doped boron p-regions which are held at ground potential (i.e., zero volts). Photoelectrons generated in these regions migrate and diffuse to the nearest potential well of a pixel the collecting phase). The vertical columns subdivided into pixels in the manner described above, by a series of conductive parallel gates that run perpendicular to the channel stops. Each line of pixels (i.e., one pixel per column) is controlled by one set of these vertical gates. A picture is read out of a CCD by a succession of shifts through the vertical registers. At each shift of the vertical section the last line of pixels transfers into a horizontal register. This register is also a CCD channel oriented at right angles to the vertical channels situated at the top and/or bottom of the device. Then, before the next line is shifted, the charge in the horizontal register is transferred to an on-chip output amplifier where charge for each pixel is converted to an output voltage. The sensitivity of the amplifier is expressed in volts per electron (approximately 1 to 4 micro-volts/electron is exhibited for most scientific CCDs). The device is then serially readout line by line, pixel-by-pixel, representing the scene of photons incident on the device.

## Buried Channel Operation

The above discussion described a surface channel CCD, since charge packets are stored and transferred along the surface of the semiconductor (i.e., at the Si-SiO<sub>2</sub> interface). problem exists with surface channel CCDs since charge can become trapped in interface traps found at the surface severely limiting CTE performance (4, 5, 6). The first surface channel CCDs fabricated exhibited CTEs of 0.98 (i.e., 98 % efficient per phase transfer), much too low for scientific work. Although different attempts have been made to passivate and reduce the density of interface states through various process schemes, it became clear early on that surface channel operation could not be used for scientific especially when small packets CCDs charge In addition, large area arrays to be developed required thousands of transfers demanding ultra-high performance, CTEs than surface channel sensors could never achieve.

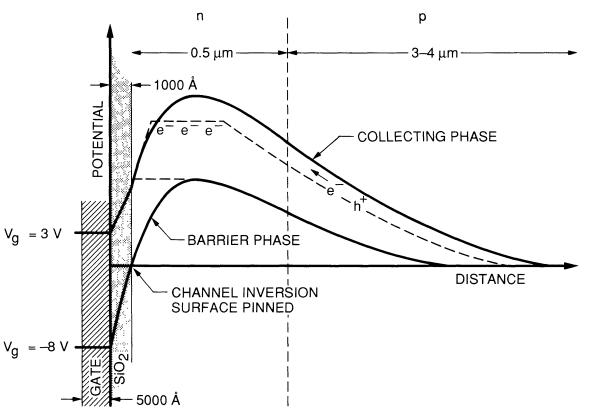

the circumvent surface state trapping problem significantly improve CTE performance the buried channel CCD was proposed (7, 8, 9, 10). In a buried channel device charge packets are confined to a channel that lies beneath the surface in the silicon. In contrast to surface channel operation, the CTE for buried channel CCDs is amazingly high. we will demonstrate in Chapter 7, efficiencies of greater than 99.999 % per pixel transfer are routinely achieved for buried channel CCDs fabricated today.

Figure 2 presents a cross-sectional view of a buried channel CCD showing a region of n-type material (typically a phosphorus implant) forming the buried channel. In comparison to a surface channel structure, the extra n-dopant reshapes the potential well so that electrons are forced to collect below the  $Si-SiO_2$  interface. Two potential wells are shown for applied gate voltages of -8 V and 3 V. As with surface channel devices photoelectrons migrate to the highest potential seen a region

Figure 1. Surface Channel MIS Potential Well

Figure 2. Buried Channel MIS Potential Well

which is now situated between the  $Si-SiO_2$  interface and n-p junction. If the gate voltage is changed from -8 to 3 V, electrons will leave the -8 V well and collect within the 3 V well. Photogenerated holes leave the silicon through the substrate contact which is referenced to ground potential (i.e., 0 V).

The potential well of a buried channel structure changes shape when signal electrons fill it (refer to the dotted potential well shown in Figure 2). Three important changes occur. First, the potential maximum (or channel potential) of the collecting phase decreases as it approaches the potential of the barrier phases. Second, the potential maximum of the well shifts towards the Third, the potential well flattens and broadens as surface. When the potential of the collecting and barrier phases become equivalent charge will spill over the barrier phases into This example of charge spreading among neighboring pixels. pixels is referred to as blooming and is when the device has reached a condition referred to as bloomed full well. mechanism of charge spreading is when charge first interacts with the surface first before blooming. This state occurs when the potential maximum of the collecting phase equals its surface This full well condition is referred to as surface Chapter 9 discusses how the CCD can be biased into full well. either state and also describes how optimum full well can be achieved.

# Inversion and Pinning

A particularly important condition develops when a phase is driven negatively such that the surface and substrate potentials become equal (this state is shown for the barrier phase in Figure 2). Under this bias condition the n-channel at the Si-SiO<sub>2</sub> interface inverts, that is, holes from the channel-stops are attracted and collect at the surface. Reducing the gate voltage further generates more holes pinning and maintaining a surface potential of zero volts. The thin layer of holes at the surface is conductive and shields the silicon layer from the gate potential fixing the potential well shape (when inverted any change in gate bias goes directly across the gate insulator). Frontside pinning or channel inversion has a profound effect on CCD performance as we will discuss in Chapters 8 and 9.

### 3. AREA ARRAY AND PIXEL SIZE

#### Early Developments

It was recognized early in the development of the scientific CCD

that the number of pixels required for most scientific imaging applications would be significantly greater than standard formats employed in commercial broadcast TV cameras (i.e., 320 (H) x 512 (V) pixels). Vidicon tubes developed and utilized for recent JPL planetary imaging missions were based on 1024 x 1024 pixel formats (e.g., the Viking vidicons cameras sent to Mars) and therefore, early development would focus on obtaining pixel counts this large. At the time (1973) it was unknown how many pixels could be packed onto a single chip. As it turned out fabricating arrays with pixel counts this many was the most challenging aspect in the development of the scientific CCD. Curiously the demand and challenge for even larger arrays today still exists. For example, astronomers always prefer larger CCDs as their telescopes continue to grow in size.

CCD development at JPL initially involved three US manufacturers: RCA, Fairchild, and Texas Instruments (TI). Fairchild was a pioneer in developing the CCD fabricating high performance buried channel devices. The sensors exhibited read noise floors of less than 30 e- rms (root-mean-square) and CTE's better than 0.99995 per transfer, a remarkable achievement considering that the CCD was invented only a few years before (Boyle's and Smith's original CCDs were surface channel and exhibited CTEs of 98 %). Fairchild CCDs were even commercially available: a 1 x 500 pixel linear CCD array and a 100 x 100 pixel area CCD array were the first devices to be offered to the scientific community at a modest cost (11). These early devices were a tremendous benefit in getting the scientific CCD off the ground. At JPL several slow-scan CCD cameras were built around Fairchild CCDs for test These early CCDs were also the first sensors used behind small astronomical telescopes. For example, in 1974 a 100 x 100 pixel Fairchild CCD was used in conjunction with a 8-inch Celestron telescope which may have produced the first CCD astronomical images of the moon and planets (i.e., "first light" for the CCD). Unfortunately the architecture philosophy that Fairchild followed and continues to do so today (i.e., interline transfer (12)) was not optimized for scientific performance primarily in achieving high quantum efficiency, an important CCD parameter to be discussed in Chapter 4.

RCA took a different approach initially: a full frame and backside illuminated CCD (to be discussed below) which in theory would achieve the highest QE sensitivity possible. RCA was developing the largest CCD at the time, a 512 (V) x 320 (H) pixel frame transfer device (13). Unfortunately, early RCA CCDs were based on surface channel technology mentioned in Chapter 2. Hence, CTE performance for these early detectors was poor and the read noise high compared to Fairchild CCDs. Also both RCA and Fairchild were concentrating on commercial formats with limited

spatial resolution, unsatisfactory for JPL and scientific needs. It became clear from these early studies that a special R & D effort was necessary to combine the best attributes of all CCD technologies known at the time. JPL then contracted Texas Instruments to work on a scientific sensor based on backside illumination, full frame, buried channel, with pixel counts equivalent to or greater that the vidicon tube. The effort between JPL and TI progressed for over a decade and is where many breakthroughs for the scientific CCD originated.

## CCD Array Shorts and Opens

The main limitation on CCD array size is directly related to the number of gate shorts and opens that result during fabrication of the sensor. Simply put, the larger the CCD the greater the probability the sensor will exhibit a short or open. These defects are usually caused by contamination, such as dust particles, that land on the CCD silicon wafers during processing. Contamination events are minimized by means of special filters filter the air that circulates through the laboratory. Large CCD arrays fabricated require at least a class 100 clean room environment (100 particles per cubic meter) or A few CCD manufacturers maintain class 1 clean rooms where human intervention is not allowed. In these labs CCDs are fabricated by robots the approach used by the Japanese at TIJ in fabricating the SXT sensor.

Several types of CCD shorts have been identified and investigated over the years. For example, shorts between clock phases is one common shorting problem (i.e., inter-level short), a serious problem related to early CCDs fabricated at TI when 3-phase aluminum gate technology was employed. A short between clock phases for these early CCDs usually resulted in a "hard short" which either destroyed the external CCD clock drivers or led to poor CTE behavior in the vicinity of the short. The functional yield was extremely low due to the shorting problem (< 0.5 %). However, a few sensors as large as 400 x 400 pixels were fabricated and were the first scientific CCDs successfully employed at astronomical observatories. For example, a 400 x 400 pixel rear illuminated aluminum gate CCD was the first sensor used in JPL's traveling CCD camera system employed at Mt. Lemmon in Arizona on the Catalina 61-inch telescope.

The aluminum gate shorting problem experienced at TI was recognized as a serious problem which would limit array sizes to no larger than 512 x 512 pixels. In addition, the reliability of the aluminum gate CCD was questionable because *latent failure shorts* were often observed (shorts that would appear with use of the device), an important concern when the sensor is used in

To circumvent the aluminum gate shorting space applications. problem TI changed to a poly silicon gate technology (14, 15) already successfully implemented by Fairchild and RCA (it appears that these groups were ahead of TI in this area of development at Since doped poly silicon was significantly less the time). conductive than aluminum an inter-electrode short was catastrophic to drive electronics and global CTE performance. silicon also had the advantage of being relatively transparent incoming photons allowing for frontside to illumination whereas aluminum gates were opaque requiring the CCD to be thinned and backside illuminated. The device yield at TI significantly improved when poly silicon gate 512 x 512 pixel CCDs were fabricated. The technology eventually led to 800 x 800 pixel versions, devices currently used by Space Telescope. Today nearly all scientific CCDs are based on poly silicon electrodes.

Another type of short that plagued early CCD development was the substrate short. A substrate short of any magnitude inevitably manifests itself as a column blemish induced by leakage current injected from the conductive gate into the signal carrying channel of the device. In fact, the majority of devices with substrate shorts would saturate the CCD due to the excessive leakage channel currents. The substrate short also impacted device yield at TI. For example, less than 2 percent of the WF/PC I CCDs passed the shorts test due in part to the substrate short. For this reason 114 lots of sensors were fabricated to satisfy WF/PC's needs (a WF/PC I lot contained 132 devices).

Triple polysilicon gate processing, used in fabricating threephase CCDs is a high yield technology and has permitted large area array CCDs to be realized. Two-level poly gate processing is used in making two and four-phase CCDs and are easier to make requiring less process steps than three-level poly. However, this CCD technology has one serious draw back, the intra-level An intra-level short is produced during fabrication when a "bridge" of poly forms between the same poly level deposited (referred to as poly stringers). The poly bridge may be caused by a speck of dust that lands on the CCD wafer during processing preventing the poly layer to be etched properly. For example, four-phase CCDs that employ double poly typically utilize the first poly level for phases 1 and 3 and the second poly level for phases 2 and 4. An intra-level short that occurs in the first level would short phases 1 and 3 resulting in poor CTE for the entire line and for all lines above the troubled site (this type of CCD blemish is referred to as a line drop-out). Triple poly gate processing eliminates this difficulty since each level is intentionally connected and bussed together forming phases 1, 2 and 3.

#### LOCOS Process

Fortunately advanced silicon processing techniques were also being developed at the same time the scientific CCD was evolving. These advancements were prompted by serious competition among silicon manufacturers world wide who were fabricating logic chips computer related hardware (e.g., RAMS, DRAMs, processors chips, etc.). These important advancements had an major impact on yield when CCD manufacturers utilized the same process recipes. For example, localized oxidation of silicon (LOCOS, a process developed at Phillips Laboratory) was optimized for CCD fabrication. The LOCOS process is based on the fact that silicon nitride can be used as a mask against thermal oxidation which becomes highly advantageous when fabricating CCDs. addition, there are certain enchants (e.g., H3PO4) that removes silicon nitride but not silicon dioxide and vica-versa. LOCOS process the CCDs insulator is based on a dual insulator system (e.g., typically 500 A of silicon dioxide and 500 A of silicon nitride). This insulating system significantly reduced the number of substrate shorts compared to a single layer of oxide (1000 A) used initially by CCD manufacturers. Today most large area array CCD manufacturers use an oxide/nitride insulator. A few CCD manufacturers use a simple oxide insulator, however, device yields are typically lower with exception of those groups who benefit from ultra-clean facilities (i.e., class The WF/PC I TI 3PCCD was built in a research laboratory (i.e., class 100) using a simple gate oxide layer, however, as indicated above tens of thousands of devices had to be fabricated to obtain a couple hundred good chips.

A common array size commercially available today is the 1024 x 1024 pixel CCD. The current yield for this array size is exceptionally high as demonstrated by several CCD manufacturers (TI, Tektronix, Loral, Kodak, Thomson, and GEC). For example, recent  $1024 \text{ x} 1024 \text{ CRAF/Cassini } 12\text{-micron pixel CCD lots using the LOCOS process exhibit a shorts yield as high as 75 % (i.e., 75 % of the CCDs don't show shorts) and a cosmetic yield without column blemishes as high as 25 % being achieved - an amazing accomplishment in contrast to early CCD lots built at TI a few years before. Even higher yields have been obtained for the new WF/PC II 800 x 800 15-micron CCD made at Loral.$

## Ultra-large CCD Arrays

CCD technology and fabrication is pushed hard when array sizes of 4 million pixels per array or greater are made. The difficulty is most apparent in the price-tag to the consumer. Although the price of the CCD as a whole increases dramatically as size increases, the cost per pixel is nearly the same. For example,

the current cost for a thinned backside illuminated and frontside illuminated Grade 1 Tektronix 512 x 512 pixel CCDs is \$6000 and \$1800 respectively (2.29 and 0.69 cents per pixel). Similar devices based on a 1024 x 1024 pixel format are \$35,000 and \$25,000 (3.34 and 2.38 cents per pixel). Still larger, the Tektronix 2048 x 2048 pixel CCDs cost \$110,000 and \$53,000 (2.62 and 1.26 cents per pixel). The Tektronix CCD family is based on a 21-micron pixel.

The 4096 x 4096, 7.5-micron pixel CCD fabricated at Loral is the largest CCD fabricated in terms of pixel count (compare this CCD to Bell Labs first CCD which was only 8 pixels long (16)). The chip is the first CCD fabricated that can compete with the resolution capability of photographic film. The resolution power of the CCD is awesome. For example, two football fields set side-by-side can be resolved to 1 inch per pixel including the side and goal zones. Looking skyward, the 4096 x 4096 pixel sensor can cover 68 arc minutes of the sky with 1 arc sec resolution (the moon extends about 32 arc-minutes). The cost of the CCD is approximately \$60,000 demonstrating the difficulty in fabrication of the device.

Tektronix fabricates the largest CCD physically, a 2048 x 2048, 21-micron pixel device occupying a single four-inch silicon wafer. Comparing the cost of the Tektronix chip to Loral's 4096 x 4096 pixel CCD it appears that they are about equally difficult to fabricate. Although the Loral CCD occupies less real estate than the Tektronix CCD the device has more pixels per unit area, a factor that also lowers device yield.

Based on todays CCD technology and yield figures it appears possible that a 8192 x 8192, 7.5-micron pixel CCD could be fabricated. This assumes that funding could be found fabricating such a hypothetical device. The cost of the CCD would be significant since only one or possibly two devices from a lot run might be obtained (the cost of a CCD lot run ranges between \$60,000 to \$120,000 depending on the CCD foundry). However, a device this large would present numerous difficulties for the user, primarily in the area of data storage. would produce, for example, over 130 million bytes of information per image assuming 16-bit encoding. Such an enormous amount of data is equivalent to a 27 million-word book or about 250 The sensor format would match that of fourhundred and nine 320 x 512 pixel CCDs. Readout time of the CCD would also present a problem. Assuming a single on-chip amplifier operating a 25 k pixels/sec, the device would require 42 minutes for readout. There are no immediate plans by any CCD group to fabricate such a device in the near future.

A trick in beating the yield problem and obtain ultra-large CCDs is to mosaic them. Several CCD groups are currently using this approach. For example, Loral fabricates four 2048 x 2048, 15-micron pixel CCDs on a four-inch wafer. The sensors are designed so that non-shorted devices can be diced, butted, and mosaiced on two edges that can be organized into a 4096 x 4096 pixel format. Packaging costs are high when using this approach since very tight tolerances are required in butting the chips in keeping the seam regions between each device to a minimum (a couple pixels can be achieved). For similar packaging efforts it may be more cost effective to fabricate a full wafer CCD rather than resorting to mosaicking.

#### Silicon Wafers

A lot run of 2048 x 2048, 15-micron Loral CCDs consists of twenty-two 4-inch wafers yielding 88 devices. Higher yields could be achieved if larger silicon wafers were utilized. Although six-inch wafers are commonly used at leading US microelectronic chip manufacturers who fabricate micro-processor and memory chips, wafers this size are not popular with American CCD Japanese groups utilize six-inch CCD lines manufacturers. primarily to satisfy the high commercial demands for video and The 1024 x 1024 pixel SXT CCD was still CCD camera markets. fabricated using six-inch wafers at Texas Instruments of Japan The yield for the SXT CCD increased significantly compared to the same CCD fabricated on four-inch wafers at TI in Dallas (TID).

Converting from a four-inch to a six-inch CCD line is expensive investment involving five to ten million dollars for new processing gear (furnaces, implanters, reticle steppers, deposition systems, facilities, etc.). Unfortunately, motivation and funds for such equipment to fabricate scientific evident in the states. Interestingly manufacturers may be forced into a six process since quality four-inch silicon may be in short supply in the future (currently six-inch material is easier to obtain than 4-inch). because non-CCD manufactures have been motivated to use larger wafers to remain competitive for yield and profit reasons. Experimental twelve-inch silicon wafers have even been grown implying that the demand for even larger wafers is on-going. appears that US CCD groups will be required to keep up with these technology trends if the scientific CCD is to survive. important to note that the Space Telescope TI 3PCCD was built on 3-inch silicon wafers, material that is virtually nonexistent today.

#### Pixel Size

Photolithography processes used in fabricating CCDs requires the precise position of a number of doped regions and interconnection patterns. These regions include implants and diffusions, contact cuts for gates, metallization and protective cover layers through which connections can be made to bonding pads. Typically seven to ten major lithographic steps using reticles or masks are required for each silicon wafer processed. For example, a basic three-phase CCD requires the following mask set: (1) field oxide (the mask that defines CCD channel and channel stops), (2) poly-1, (3) poly-2, 4) poly-3, (5) n+ mask (used in defining the source and drain regions for the reset and on-chip amplifier, (6) contact (mask that cuts oxide to make contact to poly electrodes, metal (aluminum busses that contact to poly diffusions), and (8) bond pads. There are also several optional masks that can be selected depending on application.

A mask set is designed by a CCD designer using a Computer Aided Design (CAD) terminal. For example, the 1024 x 1024 pixel CRAF/Cassini CCD was designed with AUTOCAD 10, a CAD software package developed for personal computers (PC). Next the CCD design is sent to a specialty house where a computer converts the layout and directs an electron-beam to write the CCD pattern onto aluminized glass substrates producing the mask set. Mask sets can be obtained in fairly short order, a couple weeks is typical.

There are basically two types of mask sets used in fabricating CCDs referred to as (1) contact and off-contact masks, and (2) projection masks. In contact printing the mask is in intimate contact with the silicon wafer. With an off-contact reticle there is a space a few microns between the mask and wafer (the space significantly extends the life time of the mask). Projection printing uses an expensive optical system to project the image of the mask onto the silicon at a distance. printing can achieve CCD design features of about 1-micron. Stepper masks can hold design features to about 0.2 microns, and therefore, are used when small pixel sensors are fabricated. Three-phase pixels as small as 5-microns square have been fabricated, the present limit at Loral for example.

One of the largest CCD pixels fabricated was a 52-micron square pixel designed by EG&G Reticon for JPL's High Resolution Imaging Spectrometer (HIRIS) CCD camera. The HIRIS pixel was based on a four-phase design providing 13-microns per phase. Although larger pixels were desired by HIRIS, a 52-micron pixel was felt to be the largest feasible without resorting to additional phases per pixel to transfer charge properly (64-phase CCDs have been fabricated for this purpose to achieve ultra-large well

capacities with good CTE). Pixels are limited to the HIRIS size because the potential variation beneath the phases is for the most part uniform. Hence, there are no electric fields in the middle of the phase to transfer charge from phase-to-phase as the Charge primarily moves in a CCD because of CCD is clocked. fringing fields generated by neighboring phases (17,Without fringing fields charge would sit beneath a phase and would only slowly transfer by diffusion and self-repulsion field effects (refer to Chapter 7). Fringing fields from adjacent phases extend into a phase only a few microns. Therefore, achieve good CTE the length of a phase should be limited to about 10-microns or possibly longer depending on how fast charge is transferred. Measurements made on the first HIRIS CCD exhibited a horizontal CTE problem because the length of the last clocked gate (i.e., summing well) was designed too long and required nearly a micro-sec of transfer time to dump charge to the output diode or sense node (refer to Chapter 8). In that a pixel rate of 3 Mpixels/sec was required by HIRIS the summing gate was redesigned and shortened decreasing transfer time.

# 4. QUANTUM EFFICIENCY

This property of the CCD determines the sensitivity of the device to photons incident upon it, and of course, is a very important parameter in seeing very faint objects. Quantum efficiency basically measures photon loss and includes reflection loss at the surface of the sensor, loss by the absorption in the gate electrodes, loss in the gate insulator, loss of carriers via recombination in the silicon substrate, and for the near IR and x-ray radiation lack of sufficient photon absorption in the material on which the CCD is built. Several design and process approaches have been used to minimize these losses for the CCD.

In it's early development it was discovered that the CCD could achieve high QE over a very broad spectral range including the near IR (7000-11,000 A), the visible (4000-7000 A), the UV (1000-4000 A), the extreme UV (100-1000 A) and the soft x-ray (1-100Such performance was first demonstrated by the thinned A). backside illuminated TI 3PCCD. Frontside illumination of the TI 3PCCD and other similar devices were limited to a small spectral range (the near IR, visible, and some of the x-ray spectrum). Limited coverage was due to photon absorption in the relatively thick gate electrodes. For example, at a wavelength of 4000 A, the absorption depth of a photon is only 2000 A in silicon (absorption depth is that distance where 63% of the incoming photons are absorbed, i.e., exp<sup>-1</sup>). Because the thickness of poly silicon gates are typically thicker than this (5000 A in the case of the TI 3PCCD) low QE was exhibited (a few percent at 4000 A).

The gate absorption problem worsens in the UV and peaks mid-range at 2500 A where the absorption length is only 25 A (a few atomic layers) resulting in zero QE for the CCD. Reflection of photons from the surface is also the greatest at this wavelength, approximately 70 %. Shortward of 2500 A absorption and reflection loss decrease and the top layers of the CCD become less influential on QE. However, the frontside illuminated CCD only begins to show life in the soft x-ray (shortward of approximately 25 A) where photons can once again penetrate through the gate electrodes into the active silicon.

At either end of QE response, in the near IR (11,000 A) and soft x-ray (1 A), the CCD looks transparent to incoming photons because the absorption length of the photon is much greater than the active thickness of the device. For example, a 1.06-micron photon penetrates several hundred microns in silicon resulting in a QE of a few tenths of a percent. A similar cut-off response is exhibited at the end of the soft x-ray regime (i.e., 1 A or 10 QE performance can be improved in these spectral regions by making the active cross-section of the device thicker. depletion or high resistivity CCDs are being fabricated for this These sensors are fabricated on high resistivity silicon which deepens the pixel potential wells collecting photogenerated charge made deep in the CCD. example, conventional CCDs employ 10 to 50 ohm-cm resistivity silicon resulting in depletion depths not more than 10-microns. Deep depletion CCDs on the other hand employ resistivities of 1000 ohm-cm or greater resulting in depths of tens of microns with a proportional increase in QE in the IR and soft x-ray.

## Backside Thinning

As mentioned above, thinning and backside illuminating the CCD will deliver the highest QE possible. Thinning a CCD is a simple procedure to perform. In fabricating the Space Telescope CCD the following thinning recipe was used at TI. Following wafer fabrication and die separation, a chip was mounted frontside down onto a 3-inch sapphire wafer. Then the active area on the backside of the chip was carefully masked using a hard wax. sapphire disc and CCD were then mounted onto a teflon disc about the size of a hockey puck. The puck was then lowered and immersed into a plastic drum containing acid etching solutions (hydrofluoric, nitric, and acetic acids) which in combination rapidly etches silicon (the sapphire wafer, wax, and teflon puck are immune to the acids). The drum, tilted at 45 degrees, was then rotated slowly at 30 rpm rate reversing directions every The teflon puck freely rotated in the bottom of minute or so. the drum in an opposite direction to drum rotation. The chip was thinned from an initial thickness of about 300-microns to a

thickness of 8-microns in about an hours time. Thinning essentially stopped when the epitaxial interface was reached because the etch rate of silicon significantly diminishes when low-doped, high resistivity epitaxial material is encountered. For the TI 3PCCD this rate was approximately 100 times slower, and therefore, the epitaxial interface was used as an etch stop. After thinning, the CCD was carefully removed from the drum, puck, and sapphire disc and thoroughly washed before mounting in a package.

Thinning and subsequent packaging at TI was a delicate process to perform and heavily took it's toll on sensor yield initially where many good CCD imagers were lost. Nearly 1 decade of thinning work was performed at Texas Instruments (by a single individual) for the Space Telescope effort. Thinning yields at the end of the WF/PC program were perfected to the level where only a few sensors were lost to the process.

Two major problems were associated with the thinning technique implemented at TI. First, as the CCD was thinned eddy currents set-up in the thinning drum preferentially etched the corners of The corners of the WF/PC CCDs are about 1-micron thinner than the center of the device due to this problem. characteristic led to nonuniform QE sensitivity across (for some WF/PC CCDs this detector amounted to global QE nonuniformities of greater than 500 %). Second, mechanical stresses about the active area developed causing the thinned membrane to warp typically in a concave manner (the warp was specified by JPL engineers as the potato chip factor). For some thinned devices the flatness varied as much as 100-microns due to This trait made it difficult to focus an image this problem. onto the CCD when employed in fast optical systems. corrective optics were sometimes positioned in front of the CCD to correct the aberration (telescopes faster than f/5 required To make matters worse the shape of the fixes like this). membrane would change and buckle as the device was cooled making the surface a moving target.

Fortunately thinning problems experienced at TI for the most part have been eliminated today. For example, Tektronix supports and backs the frontside of the CCD with a thick ceramic header before thinning is performed. This method guarantees that the CCD will remain flat after thinning. Also Tektronix thins the entire silicon wafer resulting in uniform thickness and QE response for individual CCDs. It is interesting to note that after the Tek device is thinned it must be electrically bonded to the package. To accomplish this the sensor is spot thinned beneath the bond pads coming in from the backside of the device (necessary since the frontside is covered with a ceramic header). The CCD is then

bonded using the "backside" of the bond pad - a cleaver trick to implement in practice.

#### Backside Accumulation

To complete the thinning task the backside surface must be treated or very low QE will be exhibited, considerably less than Immediately after thinning silicon oxidizes frontside QE. forming a native oxide layer approximately 20 A in thickness. Through a very complex process the native oxide growth causes the surface to charge positively. The positive voltage induced in the oxide layer creates a backside depletion region and a corresponding backside potential well in the silicon that attracts and collects photogenerated electrons (similar to the creation of a surface channel potential well described in Chapter The signal electrons collected eventually recombine at the surface and do not reach the frontside. In addition to this problem the native oxide surface is very susceptible to charging For example, signal charge will get trapped at the surface negating the positive oxide charge causing the backside well to shrink in size. This phenomenon leads to an increase in Over time, depending on operating temperature, the trapped charge will recombine lowering the QE back to its original level. The native oxide surface is also very sensitive to environmental smog, etc.) resulting in a QE that (humidity, unpredictable from day to day. Quantum Efficiency Hysterisis or QEH is a CCD term used to describe such behavior in CCDs. was observed for all eight Space Telescope CCDs. Unfortunately the QEH problem was not discovered until the WF/PC I instrument was assembled and tested. The dilemma severely crippled the project for QE varied more than 500 % at selected wavelengths and exposure periods (such stability is to be compared to a 1 % long term photometric stability requirement specified by the Space Telescope science team). An explanation for why the QEH problem was found so late in the WF/PC effort and its solution are discussed below.

To achieve high and stable QE the backside of the CCD must be negatively charged to drive signal electrons towards the front surface where they can be collected, transferred and detected. Four backside CCD treatment approaches are currently utilized to provide the necessary backside repelling fields for high and stable QE performance. The first method referred to as backside charging involves supplying free electrons on the native oxide surface. One method employed to accomplish the charging effect is to use an intense UV light flood (1800-2500 A). The UV photons pass through the native oxide layer and are immediately absorbed by the silicon a few angstroms from the Si-SiO<sub>2</sub> interface. Some of the photogenerated electrons created by the

UV photons have sufficient energy to escape to the back surface where they can reside creating a small surface voltage (a few tenths of a volt). The negative potential in turn attracts and accumulates a thin layer of holes (approximately 200 A depending on the doping of the epitaxial material) at the Si-SiO<sub>2</sub> interface. The gradient of holes generates an intense electric field in the silicon as high as  $10^5$  V/cm when the CCD is fully charged. If the field strength is high enough an internal QE of 100 % can be achieved at all wavelengths, an important backside state referred to as the as QE-pinned condition. For some QE-pinned CCDs the backside fields are so strong that an internal gain has been observed which generates multiple e-h pairs for each interacting photon in the UV.

Other techniques have been invented to backside charge the CCD such as corona charging (a high voltage discharge in front of the sensor), and gas charging a method that briefly exposes the CCD to an oxidizing gas such as chlorine or nitrogen monoxide gases both that promote negative surface charge buildup. The eight Space Telescope CCDs use a UV light flood while in earth orbit employing the sun as the source of UV light. The sun light is brought into the side of the instrument at right angles to the axis of the main mirror by a piece of hardware referred to as the light pipe. The light pipe was added to the WF/PC I cameras before launch to fix the QEH problem costing 5 million dollars.

The main drawback to backside charging is the charge induced will not persist for long periods of time unless the sensor is kept cold (it has been shown that sensors remain charged indefinitely at -95 C, WF/PC's nominal operating temperature). To circumvent this problem another backside treatment technique referred to as the flash gate can be used to permanently generate negative charge. This method is based on depositing a monolayer (i.e., 1atom thick on the average) of a high work function metal onto the backside of the CCD. The metal causes silicon electrons to "tunnel" through the native oxide layer and generate a surface potential equal to the work function difference between the metal gate and silicon (a few tenths of volt). Gold, platinum, and nickel have been used to achieve the QE-pinned Another important advantage of the flash gate over condition. charging is that anti-reflection coatings can be deposited on top of the gate to reduce reflection loss. backside configuration has yielded very high QEs greater than 90 % in the visible for the CCD.

Unfortunately the flash gate like backside charging is also limited and fails to maintain the QE-pinned state under high vacuum conditions. Through a complex surface process not fully understood, the vacuum environment promotes additional positive

charge buildup in the native oxide layer negating the negative charge generated by the flash gate. This collapses the internal fields in the silicon resulting in a lower QE (the device becomes To bypass this difficulty the biased flash gate was unpinned). proposed. As the name implies, the backside metal gate is biased slightly negative to compensate for the positive charge induced under vacuum conditions. Because the potential on the gate can be controlled externally, the user can control the QE of the detector and also acts as an electronic shutter. For instance, when positively biased a backside depletion well forms and charge is swept towards the backside and lost as though a shutter was When biased negatively carriers are forced to the frontside resulting in high QE. Of course the electronic shutter control described only works for wavelengths where the photon absorption depth is less than the backside potential well depth induced (i.e., applicable for blue and UV wavelengths). second generation WF/PC II camera had planned to use the biased flash gate to bypass the need to UV flood the CCDs as required by Instead WF/PC II has elected to use new frontside illuminated CCDs fabricated by Loral using phosphor coatings to achieve good blue and UV QE (see next section on phosphor coatings).

Although the original biased flash gate was based on a platinum gate other groups (e.g., Lick Observatory in collaboration with EG&G Reticon) are now using a gate material made of indium tin oxide (ITO). ITO has an interesting characteristic in that it is conductive but transparent. The Lick group uses about 80 A of ITO deposited on a base of Si-O which acts as an insulator. High QE's have been achieved with the ITO structure when biased negatively.

The forth and most popular accumulation approach at manufacturers is to dope the backside of the CCD with a very concentrated but ultra-thin layer of boron. Some CCD groups using this method are Sarnoff Laboratory, Lincoln Laboratory, Thomson-CSF, and Tektronix. The boron implant provides a permanent hole layer that generates a similar field condition at the backside of the CCD as the three backside accumulation techniques discussed above. The approach is effective obtaining high QEs in the visible and UV. For example, off-theshelf Tektronix backside illuminated CCDs deliver QEs greater than 85 % when anti-reflection coatings are also used (a simple silicon nitride layer has been successfully employed by Tektronix for this purpose). The UV response for the same detector exhibits a UV QE as high as 35 % at 3000 A.

The backside of the CCD can be doped in diverse ways depending on the processing scheme used. For example, Tektronix dopes the surface using a low-energy boron implant beam. When implanting with energetic boron atoms radiation damage is induced at the backside since silicon atoms are displaced from the lattice These displacements form trapping and recombination centers for signal electrons leading to poor QE. Therefore, to "activate" the dopant and anneal the damage the surface of the CCD must be heated to a high temperature. When heating the vacancies recombine with interstitials restoring the lattice The heating process must be selective for the device structure. must not get too high or the aluminum bus lines and bond pads on the frontside of the CCD will evaporate. Only the immediate backside surface must be heated. This has been accomplished by using a scanning high energy pulsed laser beam or rapid surface annealers.

Sarnoff Laboratory follows a backside accumulation technique developed by RCA two decades ago. Unlike TI, Sarnoff thins the entire wafer before the aluminum bus lines and bond pads are deposited. A thick border of silicon around the perimeter of the wafer is left for handling purposes to finish the device. After thinning, the wafers receive a boron implant to provide the necessary accumulation layer as described above. The wafers are then sent back to the process line where they're placed into a furnace and heated to activate the boron implant. annealing, the backside of the wafers are backed with a thick The CCD wafers then move on for aluminum supporting glass. deposition and later are diced, bonded and packaged. demonstrated by Sarnoff, the technique also achieves high QE at the same levels as Tektronix when anti-reflection coatings are also employed. For extended UV response the glass support used by Sarnoff must be thinned away to expose the bare silicon surface, a process not required by Tektronix since the supporting structure is located on the frontside of the CCD.

Although the backside boron implant technique has demonstrated high QEs in the visible and UV, the QE-pinned state (i.e., 100 % internal QE) has not been fully realized over the entire photon spectrum. QE-pinned performance is crucial for radiation imaging spectrometers where the charge generated must be totally collected without loss and measured to assess incident energy (refer to Chapter 6 on quantum yield). Backside charging has demonstrated good performance in this area promoting strong internal electric fields with a minimum backside dead layer.

# Phosphor Coatings

From the discussion above it can be seen that backside processing can significantly add to the cost of fabricating a CCD. An alternative and relatively straightforward approach used to avoid

thinning and accumulation is to vacuum deposit an organic phosphor coating on the frontside of the CCD to convert incident UV photons into longer wavelength photons. The secondary photons produced penetrate beyond the gate electrodes into the active silicon achieving relatively good QE performance. Several different types of phosphors are being used. For example, WF/PC I CCDs are coated with a coronene phosphor that absorbs UV photons shortward of 3900 A and emits new photons at 5200 A. The coronene layer has one significant draw-back in that a "QE notch" is exhibited between 3900 and 4200 A, wavelengths where coronene is not sensitive. Although the WF/PC II CCDs are backside illuminated devices the coronene layer was required because the sensors exhibited very poor UV QE since the devices were not properly backside accumulated (for reasons unknown at the time).

Interestingly coronene was directly responsible for hiding the QEH problem that plagued the WF/PC I cameras discussed above. The coronene layer was inspected at TI and JPL using a UV EPROM lamp. Inspection was required to verify that the coronene layer For example, the CCD window for some flight sensors contaminated coronene because with of temperature vacuum bake-out cycle of the sensor Therefore, each time a CCD was inspected it became backside charged from the UV light exposure. Subsequent characterization and screening of the devices at JPL didn't show QEH traits since the CCDs were unknowingly backside accumulated by the UV light. The backside charge persisted for several weeks under room temperature and argon gas conditions (the WF/PC I CCD package was back-filled with an inert argon gas). Only when the CCDs were allowed to discharge over a long period of time did QEH traits become conspicuous. QEH revealed itself for the first time when the flight WF/PC I cameras were powered and tested. coronene layer had not been utilized there would have been no reason to expose the CCDs to UV light. QEH would have then been detected when the CCDs first arrived and tested at JPL.

The QE notch exhibited by coronene can be eliminated by using a different phosphor coating referred to as *lumigen* (a phosphor coating first developed by Photometrics). Curiously lumigen is the same constituent used in commercial yellow phosphorescence "high-lighting" pens. The lumigen layer is thermally vacuum deposited at  $10^{-6}$  torr with the CCD at 80 C to a thickness of approximately 6800 A. Lumigen absorbs throughout the UV and some of the EUV (i.e., 500 to 4200 A) achieving a 100 % quantum yield emitting yellow/green photons at approximately 5300 A. QE's of 12-16 % have been achieved by the new WF/PC II lumigen coated frontside illuminated CCDs that cover a spectral range of 1200 to 4200 A. Lumigen is transparent in the visible and near IR and does not significantly influence QE performance is this region

(QE is actually higher since lumigen does act as an antireflection coating). Thicker layers of lumigen (or coronene) will extend the sensor's response further into the EUV (i.e., shortward of 500 A).

The main difficulty with phosphor coatings is they have a tendency to evaporate under high vacuum conditions. For example, at  $10^{-6}$  torr and a operating temperature above 60 C, lumigen will slowly evaporate from the CCD. The CRAF/Cassini CCD will circumvent this problem by packaging the coated sensor in a hermetically sealed package and back-filling with an inert argon gas to a half atmosphere. This configuration in conjunction with a quartz window will achieve a flat QE of 15 % from 1800 A to 4200 A under space vacuum conditions (approximately  $10^{-6}$  torr) and an operating temperature as high as 100 C. The new WF/PC II CCDs have been sealed with a magnesium fluoride package window to achieve the same QE level but to Lyman-alpha (1216 A).

Two other problems with phosphor coatings should also be noted. coated frontside illuminated CCDs exhibit reduction in MTF response (refer to Chapter 6) in the UV. characteristic is because light that is generated by the lumigen layer will scatter from the target pixel into neighboring ones. Therefore, to minimize light scattering the frontside top layers (i.e., poly gates and oxide overcoat layers) should be fabricated as thin as possible to keep the phosphor in close proximity to the active silicon. This particular problem is not as concerning for backside illuminated CCDs since the phosphor is essentially in direct contact with the silicon (separated by a native oxide Second, phosphor coatings only emit one visible photon and therefore, multiple interacting photon, generation is not possible when phosphors are used. coated devices, for example, are not used in CCD radiation imaging spectrometers.

#### Frontside Illuminated CCDs

Different CCD technologies have been invented to bypass thinning and phosphor coatings to achieve relatively high frontside QE in the UV. Virtual-phase technology has been successfully implemented at Texas Instruments for this purpose. In virtual-phase a four-step potential profile within each pixel is implemented with ion-implantation, and a single overlying gate clocks two of these potential steps to effect charge transfer (the region of the pixel which is clocked is referred to as the clocked region and the region without the poly gate is referred to as the virtual region). Since there is only one poly gate layer that overlies half of each pixel, it is possible to achieve good shortwavelength response with frontside illumination. For example,

the Galileo VPCCD achieves a 25 % QE at a wavelength of 4000 A, about a factor of five times higher than a Loral three-phase CCD. The virtual-phase device provides reasonable UV QE down to approximately 1800 A at which point the gate oxide and protective "scratch" oxide layer become opaque causing the QE to drop abruptly. The thickness of the oxide layers can be minimized in the virtual region to obtain improved UV and low-energy x-ray response as accomplished by the SXT CCD. For the SXT CCD the oxide thickness is less than 3000 A allowing x-ray energies of 500 eV and greater to be detected.

In many respects VPCCDs are more difficult to fabricate than multi-phase sensors. For example, fabricating a TI VPCCD requires at least 14 mask sets in patterning the levels for the device. In comparison, a simple four-phase CCD requires half that number. In addition, the various implants employed in a virtual-phase pixel must be critically aligned with sub-micron accuracy where multi-phase pixels do not require such precision. Currently TIJ is the only manufacturer that knows how to make virtual-phase CCDs.

In general, VPCCDs when utilized in low-signal applications exhibit relatively poor CTE performance compared to multi-phase The difficulty has been traced to spurious potential pockets which trap charge in the signal channel because of improper potential well shape within the pixel defined by the As mentioned above, alignment of the implants is crucial for this technology to work, and small misalignments often create potential pockets (or bumps) which trap charge. This problem was in part responsible for the need to fabricate 39 lots of VPCCDs for the Galileo effort to obtain the single CCD unit now in space. Single clock operation is an important feature that virtual-phase technology offers. Unfortunately, the inflexibility of this virtue has often proved disadvantage for low-signal applications. Many CTE problems associated with multi-phase CCDs have been solved by manipulating the clock phases to collapse CTE pockets located in the signal channel (refer to Chapter 7). Many of the potential wells in a virtual-phase pixel are defined by implants not external gates, so the user cannot control them to achieve optimum CTE.

Open pinned-phase (OPP) CCD technology is similar to the virtual-phase CCD. An OPP CCD is constructed exactly as a three-phase CCD except that the third level of poly is not deposited leaving a portion of the pixel open to UV photons. In place of the third phase, two implants are incorporated. The first implant adds more phosphorus to the buried channel increasing the channel potential for signal charge to collect. The second implant, a concentrated but very shallow implant of boron, pins the surface

potential at the Si-SiO<sub>2</sub> to substrate potential (the conductive layer is internally connected to the channel stops which are connected to ground). This implant is important to assure that the potential well beneath the open region remains fixed as phases 1 and 2 that neighbor the open-phase are clocked. implants are self-aligned by poly levels one and two. An OPP pixel is typically designed so that phases 1 & 2 occupy half the pixel whereas the open-phase occupies the other half. Other arrangements are possible depending ful1 on well and performance desired. In OPP CCD technology only the vertical registers employ the open phase and two extra implants. horizontal registers always include the third poly level since QE performance for this register is not important. Although a scientific OPP CCD has not been successfully fabricated several three-phase CCD groups are pursuing the idea to avoid thinning The CUBIC CCD mentioned and phosphor coatings. introduction is based on OPP technology.

An alternative approach to OPP is to deposit a ultra-thin conductive gate within the OPP region that can be clocked to avoid implants. Several gate materials are possible candidates. A straightforward processing approach is to deposit a thin layer of poly silicon. CUBIC CCDs will attempt to deposit gates as thin as a few hundred angstroms for this purpose.

Lastly we should mention that transparent gate electrodes can be used to achieve good frontside QE. For example, Kodak has developed a ITO gate electrode process which has yielded good blue and UV QE.

#### 5. Quantum Yield

Quantum yield is defined as the number of e-h pairs generated per interacting photon or particle. Multiple electrons are generated for photons shortward of 3000 A. For photon energies greater than 10 eV (i.e., 1000 A) the quantum yield is simply equal to the energy of the photon (eV) divided by 3.65 eV/e-. Therefore, by measuring the charge generated of an interacting photon one can determine its energy through this relationship. then be referenced back to the chemical element liberated the photon initially (i.e., spectroscopy). radiation imaging spectrometers (CCD-RIS) are used for this purpose and demand near perfect performance in read noise, CCE, and CTE, characteristics to be reviewed in Chapters 6, 7 and 8. The energy resolution or accuracy in which a CCD can measure the energy of a photon is highly dependent on these parameters.

As indicated above it takes 3.65 eV of energy on the average to produce a single e-h pair for energetic photons interacting with the CCD. If all the energy of the photon were used to produce eh pairs directly, there would be no statistical variation in the amount of charge generated by the event. However, a finite amount of energy is transferred to the silicon lattice by non e-h giving rise to (thermal), processes a small statistical difference in the number of e-h pairs actually generated. uncertainty is characterized by the Fano-factor originally formulated by U. Fano in 1947 to describe the uncertainty of the number of ion-pairs produced in a volume of gas following the absorption of ionizing radiation. Fano-noise (in rms e-) given empirically by (F x S(e-)).5 where F is the Fano-factor (0.1) and S(e-) is the charge generated by a photon. example, a 5.9 keV x-ray photon generates 1620 e- with a Fanonoise of 13 e- rms. For a CCD to exhibit Fano-noise limited performance its read noise must be less than the Fano-noise generated by the interacting photons. Note when the energy of the x-ray decreases the CCD read noise must also decrease for the sensor to remain Fano-noise limited. As discussed in Chapter 8, noise floors of 1 e- rms can be achieved allowing Fano-noise limited performance to cover the soft x-ray region and a part of the EUV spectrum.

## Proton Radiation Imaging Spectrometers

Frontside illuminated CCDs have been recently calibrated to measure the energy of incident protons and other high energy When protons, for example, pass through a CCD they leave an ionizing trail of e-h pairs as the proton interacts with silicon atom orbital electrons. The charge generated depends on the loss of energy deposited in the photoactive thickness of the CCD (i.e., the thickness of the epitaxial layer). For example, a 1 MeV proton has a range of 15.67 microns in silicon and deposits 500 keV of energy in the first 10-microns, a typical epitaxial thickness. The remaining 500 keV is deposited in the substrate of the sensor. The amount of charge collected by pixels is simply equal to this energy (500 keV) divided by 3.65 eV/e- yielding 137,000 e-. The charge generated by a 10 MeV proton in 10-microns is only 23,000 e- since its stopping power (energy deposited per unit distance) is less than a 1 MeV proton. A 10 MeV proton has a range of 697-microns in silicon. Less signal is generated for higher energy protons.

A proton QY curve (charge generated as a function of proton energy) for normal incident protons has been experimentally generated using a SXT TI VPCCD over an energy range of 50 keV to

10 MeV (protons were supplied by Cal Tech's Van De Graff ion accelerator). A peak response in QY occurs at 800 keV where 210,000 e- per interacting proton is measured. For energies less than 800 keV the QY response falls because: (1) less charge is generated since proton energy is smaller, and (2) a significant portion of the protons energy is lost in the overlying frontside gate structures (the QY response drops to zero at 50 keV where the protons range is equal to the thickness of the oxide layer). The QY above 800 keV is measurable for proton energies up to about 1 GeV. However, above 50 MeV it becomes difficult for the CCD to discriminate between proton energies since the stopping power is nearly the same over a 10-micron region (e.g., a 100 MeV proton generates only 1.61 times more charge than a 200 MeV proton).

The limiting energy resolution (or energy straggling) for the CCD in theory should be limited by Fano-noise, however, measurements performed with the SXT sensor showed a much greater uncertainty. For these experiments the problem was traced back to Cal Tech's proton source where straggling energies of 30 to 70 keV (FWHM) were measured, significantly greater than Fano-noise. Future QY tests will therefore utilize a monoenergetic proton beam to measure the CCDs true energy resolution.

## 6. CHARGE COLLECTION EFFICIENCY (CCE)